Forward-looking: 3D chip stacking technology has yet to arrive in a big way, with only Intel Foveros reaching the market in Lakefield CPUs, and some Zen3-with-vertically-stacked-cache products waiting in the wings. But at this year's Hot Chips symposium, AMD is already laying out where it intends to go from here, with ambitious ideas on how to apply the technology.

The 3D V-Cache shown off by AMD at Computex is the (relatively) simple addition of further L3 cache to a Ryzen 9 5900X, bringing around a ~15% performance uplift in games. The 3D-stacking arrangement let AMD use a production process that allows for more densely packed SRAM for the upper die, fitting 64 MB in the space directly above the 32 MB on the base die that had to be silicon suitable for both cache and compute.

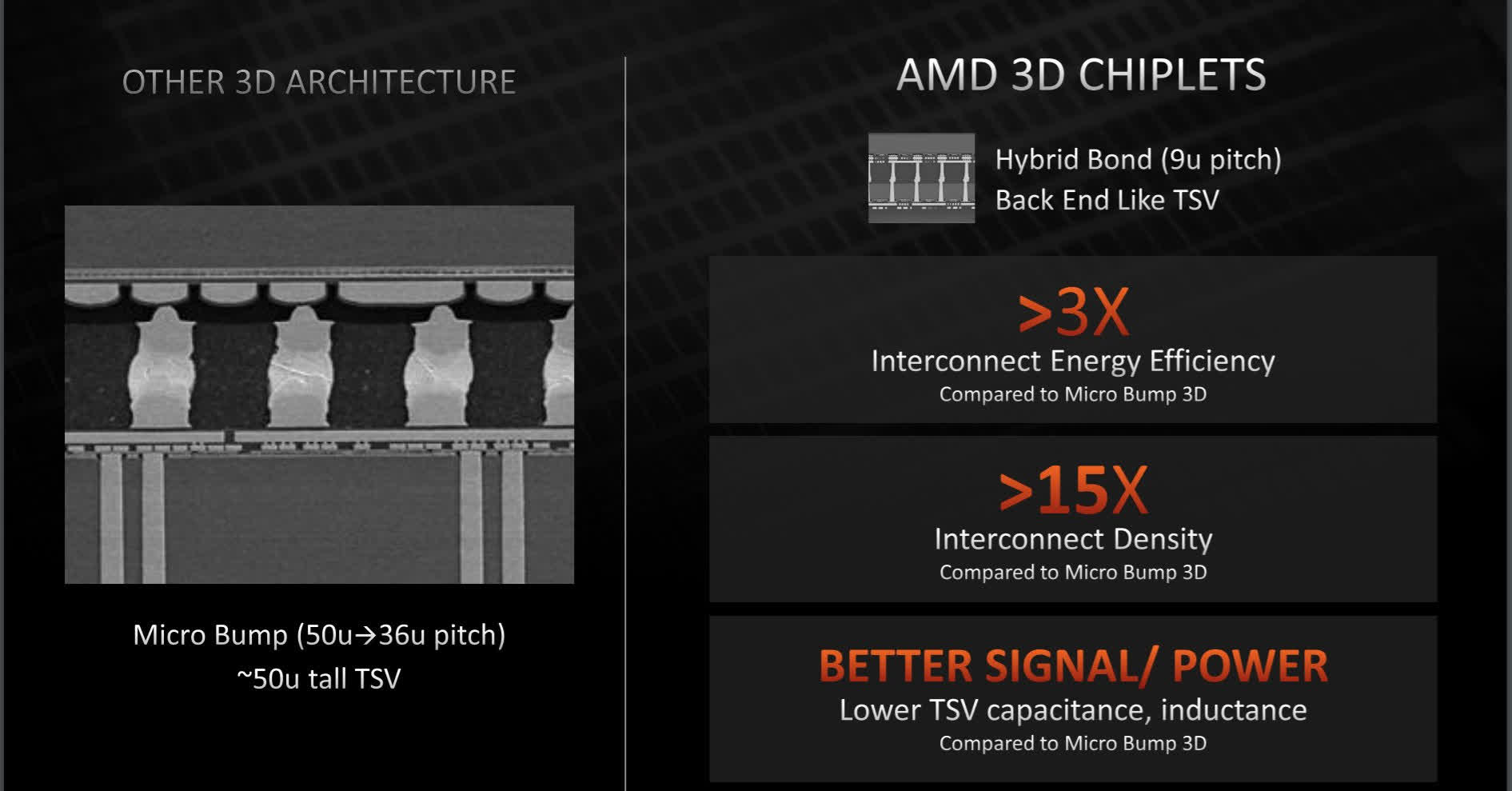

This was all done using through-silicon vias (TSVs), connected with direct vertical copper-to-copper connections that pack far closer together than "traditional" microbump technology.

AMD claims a 9 micron bump pitch for their hybrid direct bonding technology; by comparison, Intel Foveros was working on the order of 50 microns when implemented in Lakefield, the main point of comparison used for AMD's claim of 3x efficiency gains and 15x higher density with its interconnects compared to the conspicuously unspecified "other 3D architecture."

Team Blue also have a pitch of 36 microns quoted for their upcoming Foveros Omni technology to be used in Meteor Lake CPUs, and 10 microns in Foveros Direct, a hybrid solution that more directly competes with what AMD's showing off here.

However, both are only slated to arrive in 2023, while AMD have stated that their 3D-stacked Ryzen chips will be in mass-production by the end of this year.

The company is also working with TSMC on more complex 3D stacking designs, with the ambition to stack CPU cores on one another, splitting macroblocks of a CPU (such as lower levels of cache) between different layers, or even going down to the level of circuit slicing.

Stacking compute silicon in particular brings unique difficulties in providing power to higher dies and removing heat from lower ones – one of the reasons why AMD's 3D V-Cache is only layered on top of the base die's cache, leaving the CPU cores alone.

Of course, all of this depends on how much improvement can be brought in power, performance, area and cost (PPAC) metrics – and, of course, if TSMC can continue to deliver their advanced packaging techniques in mass production.